Αυτό το tutorial σκοπό έχει να γνωρίσουμε το Autologic II το οποίο μας επιτρέπει να συνθέσουμε και να βελτιώσουμε τις VHDL ή VERILOG HDL σχεδιάσεις και να τις δούμε με την τεχνολογία που επιθυμούμε.

LIBRARY ieee , arithmetic ;

USE ieee.std_logic_1164.ALL ;

USE arithmetic.std_logic_arith.ALL ;

Προτείνεται να δημιουργήσουμε έναν υποκατάλογο για να τοποθετούμε όλα τα αρχεία που σχετίζονται με το Autologic II , π.χ. autolog . Πηγαίνουμε στο νέο κατάλογο με την εντολή :

$ cd autolog .

Δημιουργούμε έναν υποκατάλογο για να τοποθετούμε τα VHDL αρχεία (vhdl),$mkdir src. Τα ονόματα των αρχείων των σχεδιάσεων πρέπει να έχουν το όνομα της οντότητας με την κατάληξη .vhdl .

Δημιουργούμε δύο υποκαταλόγους, έναν για τοποθετούμε τα δικτυώματα (netlist) και ένα για να τοποθετούμε τα αρχεία EDDM

$mkdir netlist

$mkdir eddm

Δημιουργούμε μία τοπική βιβλιοθήκη : $ qhlib <directory_pathname>.Για παράδειγμα:

$ qhlib work

Κάνουμε map την βιβλιοθήκη : $ qhmap <logical_name> <path>.Για παράδειγμα, αν το τρέχον directory είναι το autolog:

$ qhmap work ./work

Ο υποκατάλογος work θα δημιουργηθεί αυτόματα κάτω από τον autolog. Η εντολή qhmap γράφει ένα αρχείο αρχικοποίησης, το οποίο καλείται quickvhdl.ini και περιγράφει το περιβάλλον εργασίας μας. Μπορούμε να ελένξουμε την ύπαρξη του work και του αρχείου .ini δίνοντας την εντολή ls στο unix prompt.

Κάνουμε compile το αρχείο VHDL , ορίζοντας το στάνταρ 93 σαν επιλογή

$ qvhcom –93 –synth –nosynchk <filename>.vhdl .

Μηνύματα που αφορούν την δουλειά του compiler, θα εμφανισθούν. Αν δεν υπάρχουν λάθη, τα μηνύματα θα δείξουν η οντότητα (entity) και η αρχιτεκτονική (architecture) έχουν γίνει compiled.

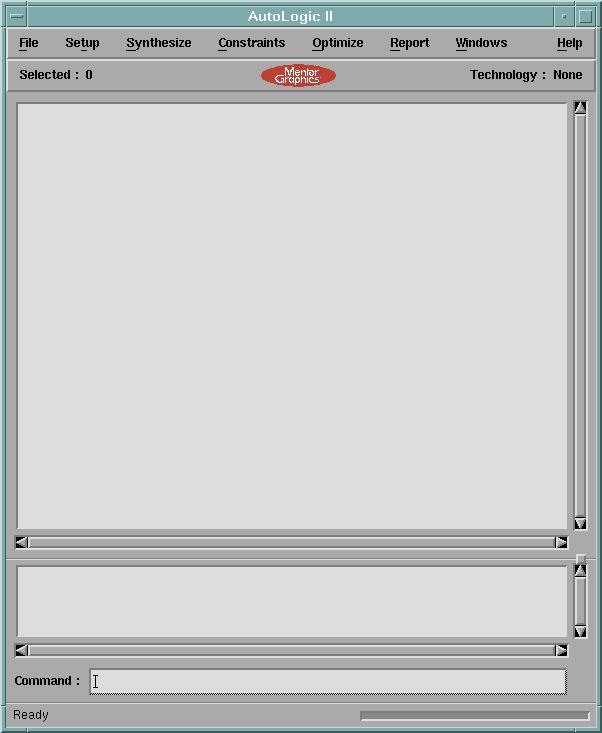

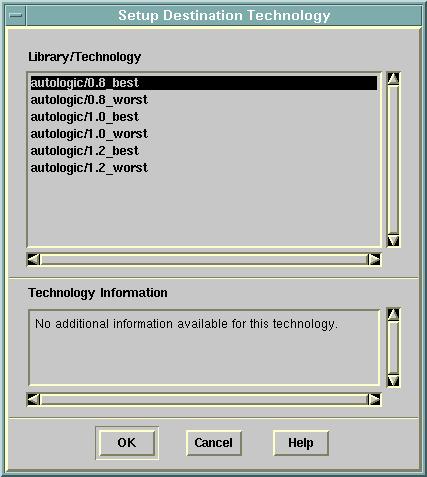

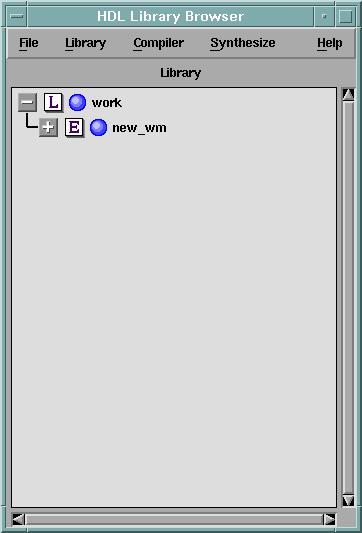

Το βασικό παράθυρο του Autologic II θα εμφανισθεί

Eικόνα 1

3. Για σχεδιάσεις VHDL : Από το μενού του Autologic II επιλέγουμε : File ->Read New INI File και επιλέγουμε quickvhdl.ini.

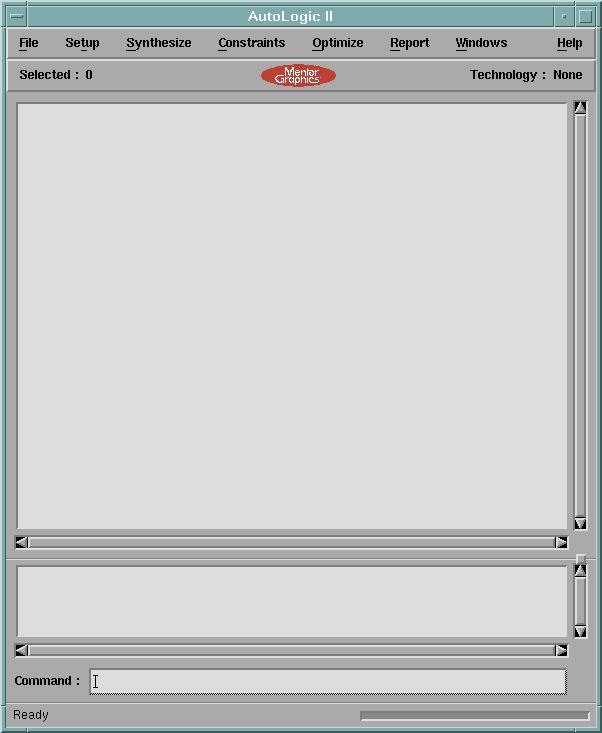

4. Για VERILOG σχεδιάσεις επιλέγουμε : File -> Open -> Design και εμφανίζεται το παρακάτω παράθυρο

Εικόνα 2

Επιλέγουμε το όνομα της σχεδίασης και το File Format το επιλέγουμε ως Verilog

και κάνουμε κλικ στο ΟΚ. Αυτό θα συνθέσει την verilog σχεδίαση και στο τέλος

θα εμφανισθεί το παράθυρο Design browser.

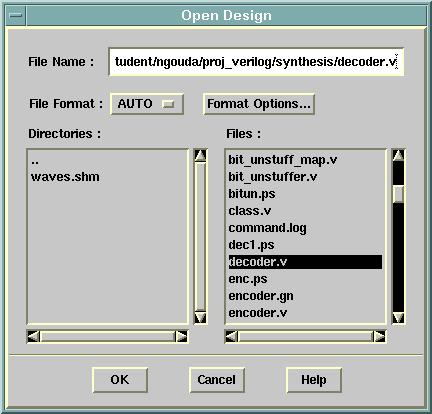

Επιλέγουμε Setup > destination technology, και επιλέγουμε την βιβλιοθήκη

στόχο.

Εικόνα 3

Οι επόμενες τρεις διαδικασίες είναι μόνο για VHDL σχεδιάσεις :

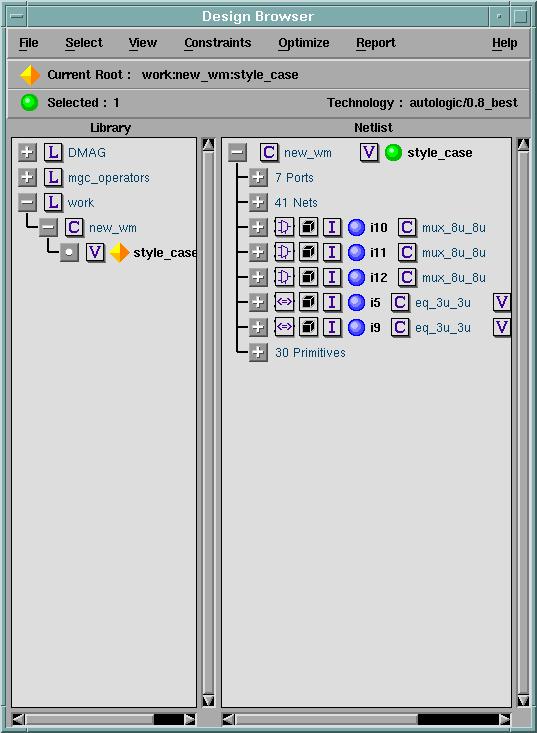

Το παράθυρο VHDL Library Browser θα εμφανισθεί όπως φαίνεται στην εικόνα 4. Αυτό παρουσιάζει τις σχεδιαστικές μονάδες (design units) που περιέχονται στην βιβλιοθήκη work. Κάνοντας κλικ στο ‘+’ δίπλα από την κάθε οντότητα, μπορούμε να δούμε τις σχετιζόμενες αρχιτεκτονικές.

Εικόνα 4

Πρέπει να δούμε τα μηνύματα που παρέχουν πληροφορίες για την σύνθεση και στο τέλος του τρεξίματος της σύνθεσης, θα ανοίξει αυτόματα το παράθυρο Design Browser, όπως φαίνεται στην εικόνα 5. Το παράθυρο που βλέπουμε αφορά ένα παράδειγμα ενός πλυντηρίου , το οποίο δίδεται αργότερα.

Εικόνα 5

Στο παράθυρο Design Browser το Current Root είναι library/cell/view. Για το παράδειγμά μας θα είναι work:new_wm:style_case.

Μπορούμε να διαλέξουμε αντικείμενα από το current root χρησιμοποιώντας το παράθυρο Netlist. Η λειτουργία των εικονιδίων είναι ίδια με το παράθυρο VHDL Library Browser. Επίσης μπορούμε να κάνουμε ενέργειες όπως σε ένα επιλεγμένο αντικείμενο, όπως : Reports -> Design -> Area.

5. Βελτιστοποίηση (Optimization)

Πριν κάνουμε βελτίωση (optimizing), πρέπει να σιγουρευτούμε ότι όλα τα αντικείμενα του Netlist είναι μη-επιλεγμένα. Από το παράθυρο Design Browser επιλέγουμε : Unselect All.

Για να κάνουμε map τις σχεδιάσεις μας στο Xilinx FPGA, πρέπει να προσθέσουμε Ι/Ο buffers σε όλες τις πόρτες. Από το μενού του Autologic II επιλέγουμε: Optimize -> Optimize ->Add/Remove IO και επιλέγουμε All ports και add. Στην συνέχεια προχωράμε όπως παρακάτω.

Για βελτιστοποίηση χώρου (optimize area) επιλέγουμε από το μενού του Autologic II : Optimize -> Optimize -> Area και εν συνεχεία την επιλογή για μικρή προσπάθεια (low effort). Η επιλογή για μεγαλύτερη προσπάθεια θα δώσει πιο βελτιωμένο χώρο αλλά παίρνει περισσότερο χρόνο. Για να ελένξουμε αν υπάρχουν τυχόν προβλήματα επιλέγουμε : Reports -> Design -> Area.

Για βελτιστοποίηση λειτουργίας (optimize for performance): Για να ορίσουμε το ρολόι, αν αυτό είναι εσωτερικό, το επιλέγουμε από το Netlist του παραθύρου Design Browser , κάνοντας κλικ στην αντίστοιχη μπλε μπάλα. Από το μενού του Autologic II επιλέγουμε : Constraints -> Add Constraints -> Clock και μπορούμε να δούμε ότι το πραγματικό και το ιδανικό ρολόι έχουν το ίδιο όνομα όπως το όνομα της επιλεγμένης πόρτας. Οι ορισμοί (definitions) μας θα ενσωματωθούν στην επιλεγμένη πόρτα. Αν από πριν είχαμε ορίσει και άλλα ιδανικά (ideal) ή πραγματικά ρολόγια, θα μπορούσαμε να ενσωματώσουμε ένα από αυτά στην επιλεγμένη πόρτα κάνοντας browsing στην λίστα των πιθανοτήτων (possibilities).

Μπορούμε να επαληθεύσουμε τον ορισμό του ρολογιού, επιλέγοντας από το μενού του Autologic II : Reports -> Constraints.

Για να δούμε τα αποτελέσματα της αναφοράς χρόνου (timing report) πριν από την βελτιστοποίηση, για να κάνουμε σύγκριση, επιλέγουμε από το μενού του Autologic II : Reports -> Design -> Timing Path.

Το default path είναι το worst timing path. Μπορούμε να επιλέξουμε multiple path για το path type.

Από το μενού του Autologic II επιλέγουμε : Optimize -> Optimize -> Timing. Διαλέγουμε την επιλογή low effort για να πάρουμε γρήγορα αποτελέσματα. Το παράθυρο Design Browser θα ανανεωθεί (refreshed).Για να ελένξουμε αν υπάρχει κάποιο πρόβλημα, επιλέγουμε : Reports -> Design ->Timing.

Μπορούμε να μετατρέψουμε το constraints κάθε πόρτας, από την επιλογή Netlist του παραθύρου Design Browser και να κάνουμε πάλι την αναφορά (report).

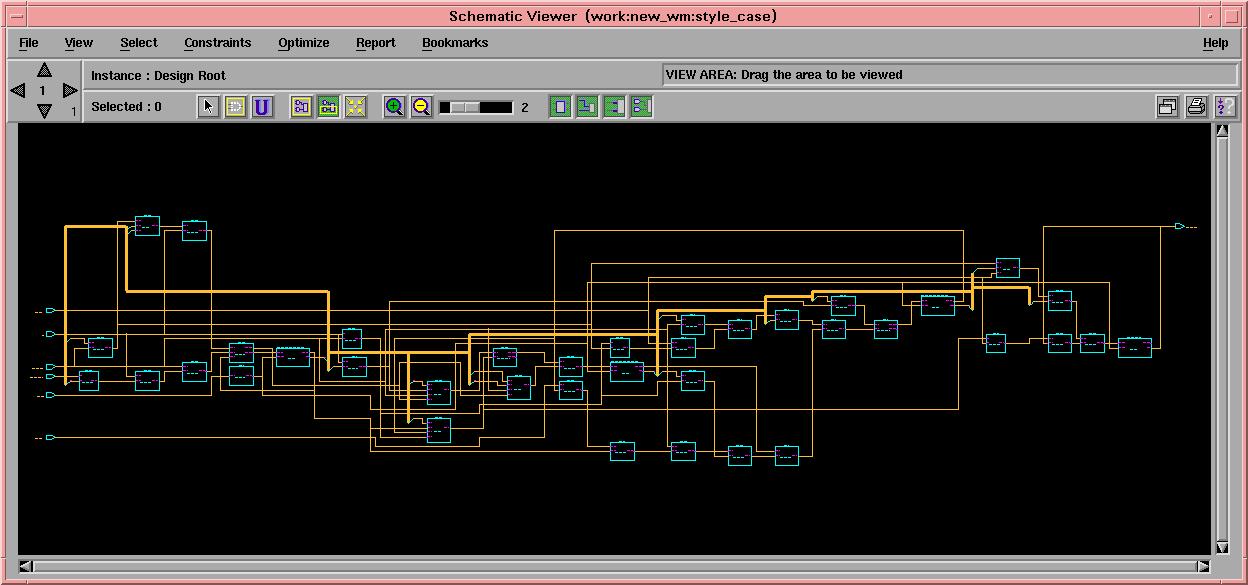

Για να δούμε το σχηματικό από το μενού του Autologic II επιλέγουμε :

Report -> schematic -> window.

Το παράθυρο Schematic θα εμφανισθεί, όπως φαίνεται στην εικόνα 6.

Εικόνα 6

Setup -> Schematic Option

Εξ ορισμού ο μέγιστος αριθμός instances per schematic sheet είναι 80, το μέγεθος του χαρτιού είναι Α και μία σελίδα ανά σχηματικό, έτσι ώστε πρέπει να δώσουμε 1 στην επιλογή Numsheet αν θέλουμε να τυπωθεί ολόκληρο το σχηματικό σε μία σελίδα.

Εξομοίωση EDDM σχηματικού χρησιμοποιώντας το QuickSim II:

Καλούμε το Mentor Graphics Design Manager, και κάνουμε κλικ στο εικονίδιο DVE. Τρέχουμε το DVE και σώζουμε το Design Viewpoint πριν καλέσουμε το QuickSimII. Αν θέλουμε να δούμε το σχηματικό πάμε στο Design_arch, κάνουμε κλικ στο DESIGN SHEET στο Session_Pallete και πάμε (navigate) στην σχεδίασή μας και κάνουμε κλικ στο ΟΚ.

Standard Cell Autolayout:

Καλούμε το IC station κάνοντας κλικ στο εικονίδιο cmosn_ic του Design Manager.

Παρακάτω είναι ένα παράδειγμα πηγαίου αρχείου, μίας σχεδίασης ενός ελενκτή πλυντηρίου, το οποίο ονομάζεται new_wm.vhdl :

LIBRARY ieee,arithmetic ;

Use ieee.std_logic_1164.ALL ;

Use arithmetic.std_logic_arith.ALL ;

ENTITY new_wm IS PORT (clk : IN std_ulogic ;

ober : IN BOOLEAN ;

coin : IN BOOLEAN ;

double : IN BOOLEAN ;

T : IN BOOLEAN ;

reset : IN std_ulogic ;

count : OUT bit ) ;

END new_wm ;

ARCHITECTURE style_case OF new_wm IS

TYPE states IS (idle, soak, wash, rins, spin, espera);

SIGNAL present_state : states := idle ;

BEGIN

Washing : PROCESS (clk)

BEGIN

IF (clk = ‘1’ AND clk’LAST_VALUE = ‘0’) THEN

IF (reset = ‘0’) THEN

present_state <= idle ;

ELSE CASE present_state IS

WHEN idle => IF coin THEN present_state <= soak ;

ELSE present_state <= idle ;

END IF;

WHEN soak => IF T THEN present_state <= wash ;

ELSE present_state <= soak ;

END IF;

WHEN wash => IF T THEN present_state <= rins ;

ELSE present_state <= wash ;

END IF ;

WHEN rins => IF (T AND double)

THEN present_state <= wash ;

ELSE CASE T IS

WHEN TRUE => present_state <= spin;

WHEN FALSE => present_state <=rins;

END CASE ;

END IF;

WHEN spin => IF T THEN present_state <= idle ;

ELSE CASE ober IS

WHEN TRUE => count <= ‘0’ ;

present_state <= espera ;

WHEN FALSE => present_state <= spin ;

END CASE;

END IF;

WHEN espera => IF (ober) THEN present_state <= espera;

ELSE count <= ‘1’ ;

present_state <= spin ;

END IF ;

END CASE ;

END IF ;

END IF ;

END PROCESS washing ;

END style_case ;