XILINX FPGA DESIGN WITH AUTOLOGIC II

Αυτό το κείμενο σκοπεύει να μας οδηγήσει στην χρήση των εργαλείων της Mentor Graphics για την σχεδίαση και εξομοίωση κυκλωμάτων. Αυτά τα εργαλεία περιλαμβάνουν QuickVHDL, Autologic, Design Architect, Design Manager και Xilinx utilities. Θα δούμε πως κάνουμε compile τις σχεδιάσεις, πως δημιουργείται το σχηματικό και εξομοιώνεται και τρέχει η σχεδίαση στο XC4003 PLD.

Δημιουργία ενός μοντέλου VHDL

Δημιουργούμε ένα κατάλογο εργασίας δίνοντας στο unix prompt την εντολή:

mkdir directory_name

Αυτό θα είναι το directory από το οποίο θα τρέξουμε τα εργαλεία της Mentor Graphics.

Δίνουμε την εντολή : setenv MGC_WD path, όπου path είναι η διαδρομή από το δικό μας root directory μέχρι τον κατάλογο εργασίας που δημιουργήσαμε στο προηγούμενο βήμα. Αυτή την εντολή μπορούμε να την δώσουμε στο αρχείο ‘ .cshrc’ για να αποφύγουμε να την δίνουμε κάθε φορά που συνδεόμαστε (log on) στον υπολογιστή.

Πληκτρολογούμε το παρακάτω αρχείο παράδειγμα, σε ένα text editor και το σώζουμε σαν “ sample1.vhd”. Αυτό το πρόγραμμα είναι ένα διάγραμμα καταστάσεων, όπως φαίνεται στην εικόνα 1.

εικόνα 1

entity statemachine is

port (clk , x : in bit;

y : out bit);

end statemachine;

architecture datapath of statemachine is

type state is (state0, state1, state2, state3);

signal state : states := state0;

begin

--output y based on state

y <= ‘1’ when state = state0 and x = ‘1’ else ‘0’ ;

s:

process (clk)

begin

if clk ‘ event and clk = ‘0’ then

case state is

when state0 =>

state <= state1;

when state1 =>

state <= state2;

when state2 =>

state <= state3;

when state3 =>

state <= state0;

end case;

end if;

end process;

end;

Compile VHDL models with QuickVHDL

Το QuickVHDL είναι ένα εργαλείο που μεταφράζει (compile) VHDL κώδικα σε ένα εξομοιώσιμο μοντέλο. Αφού το μοντέλο έχει γίνει compile μπορεί να εξομοιωθεί χρησιμοποιώντας τον QuickVHDL simulator ή να φορτωθεί στο Autologic.

Πληκτρολογούμε : qvlib work στο unix command prompt για να δημιουργήσουμε μία βιβλιοθήκη εργασίας. Αυτή η εντολή δημιουργεί ένα κατάλογο ο οποίος ονομάζεται work και περιέχει τα αρχεία που χρειάζονται για να εξομοιώσουν την σχεδίαση χρησιμοποιώντας το QVSim.

Πληκτρολογούμε : qvcom sample1.vhd –synth για να δημιουργήσουμε μοντέλο VHDL για σύνθεση. Το μοντέλο θα αποθηκευθεί στον κατάλογο sample1, ο οποίος βρίσκεται ακριβώς κάτω από τον κατάλογο work, που δημιουργήσαμε στο προηγούμενο βήμα.

Σημείωση: Δεν πρέπει να διαγράφουμε, μετακινούμε, αντιγράφουμε ή συντάσσουμε αρχεία που βρίσκονται στον κατάλογο ‘sample1’ χρησιμοποιώντας εντολές του Unix. Αν χρειαστεί να διαγράψουμε αρχεία, χρησιμοποιούμε την εντολή qvdel model_name από τον κατάλογο εργασίας ή χρησιμοποιούμε το Design Manager για να το διαγράψουμε.

Σύνθεση κυκλώματος με το AutoLogic II

Το Autologic II είναι ένας επεξεργαστής δικτυωμάτων (netlist processor). Συνθέτει το μοντέλο χρησιμοποιώντας λογικές εξισώσεις και αντιλαμβάνεται αυτές τις εξισώσεις χρησιμοποιώντας λογικά εξαρτήματα από μία technology-specific βιβλιοθήκη για να ‘χτίσει’ την σχεδίαση. Επίσης μπορεί να κάνει διάφορες βελτιώσεις στην σχεδίαση για να εξοικονομήσει χώρο ή να αυξήσει την απόδοση της επιλεγούσας τεχνολογίας. Για να ξεκινήσει το Autologic II, πληκτρολογούμε : alui στο Unix command prompt.

Φορτώνοντας τα μοντέλα VHDL σχεδίων

Χρησιμοποιώντας το ποντίκι, επιλέγουμε από το μενού στην κορυφή της οθόνης File -> Open -> Design .

Επιλέγουμε το αρχείο sample1.vhd όπως φαίνεται στην εικόνα 2.

εικόνα 2

Επιλογή της Destination Technology (Xilinx 4000 Family)

Από το μενού επιλέγουμε : Setup -> Destination Technology και από την παρακάτω λίστα των βιβλιοθηκών σύνθεσης που εμφανίζεται στο Destination Technology dialog box, επιλέγουμε : xc4k/default , και κατόπιν κάνουμε κλικ στο ΟΚ.

Library / Technology

sample_lib

scna20orbit_fast

scna20orbit_nom

scna20orbit_slow

xc4k/default

altera/default

Αυτό θα φορτώσει την βιβλιοθήκη Xilinx, που θα χρησιμοποιηθεί στην δημιουργία των σχηματικών. Η βιβλιοθήκη Xilinx περιέχει τα απαραίτητα λογικά εξαρτήματα για την σύνθεση των σχεδιάσεων στην XC4003 και άλλων FPGA της σειράς Xilinx4000.

Σύνθεση του δικτυώματος του κυκλώματος (Circuit Netlist)

Από το μενού επιλέγουμε : Synthesize -> Synthesize VHDL Design . Ένα dialog box, όπως αυτό της εικόνας 3, θα εμφανιστεί στην οθόνη.

Αυτό θα δημιουργήσει ένα unoptimized δικτύωμα το οποίο μπορεί να χρησιμοποιηθεί για την εξομοίωση της σχεδίασης.

εικόνα 3

Βελτιώνοντας την σχεδίαση του κυκλώματος

Από το μενού στην κορυφή της οθόνης επιλέγουμε : Optimize -> Optimize Design .

Ένα dialog box όπως αυτό της εικόνας 4, θα εμφανιστεί.

Σημείωση: Η βελτίωση για χώρο (Optimizing for Area) θα δημιουργήσει μία σχεδίαση η οποία χρησιμοποιεί τον ελάχιστο αριθμό λογικών πυλών για να εκτελέσει τις επιθυμητές λειτουργίες της σχεδίασης.

εικόνα 4

Για άλλη μία φορά επιλέγουμε : Optimize -> Optimize Type . Αυτή τη φορά επιλέγουμε : Add I/O Buffers από το dialog box.

Σημείωση: Βελτιώνοντας για Ι/Ο cells θα προσθέσει buffer εισόδου και εξόδου σε όλες τις γραμμές που έρχονται μέσα ή βγαίνουν από την σχεδίαση.

Βελτιώνοντας ξανά για χώρο (area), αλλά αυτή τη φορά επιλέγοντας “Map” από τις επιλογές “Area Optimization Options”. Αυτό θα προσθέσει εξωτερικά Ι/Ο pads στις πόρτες εισόδου και εξόδου.

Save the design netlist and/or schematic

Το σώσιμο της σχεδίασης θα κάνει το Autologic να δημιουργήσει αρχεία δικτυωμάτων (netlist) και (προαιρετικά) ένα σχηματικό. Από το μενού επιλέγουμε:

File -> Save -> Eddm.

Το Save Design κουτί διαλόγου θα εμφανιστεί , όπως φαίνεται στην εικόνα 5.

εικόνα 5

Όταν σωθεί η σχεδίαση, ένας νέος κατάλογος που ονομάζεται “eddm” θα προστεθεί κάτω ακριβώς από τον κατάλογο εργασίας. Όλα τα καινούργια αρχεία που παράγονται από το Autologic II θα τοποθετούνται στον καινούργιο αυτό κατάλογο. Η δομή του καταλόγου είναι η ακόλουθη.

Σημείωση: Από την στιγμή που το Autologic II δημιουργεί αυτά τα αρχεία στην μνήμη κατά την διάρκεια της λειτουργίας, όλες οι αλλαγές θα χαθούν αν δεν σωθούν πριν την έξοδο από το πρόγραμμα.

Βλέποντας την σχεδίαση με το Design Architect

Το Design Architect είναι ένα εργαλείο για να βλέπουμε τα σχηματικά που παράγονται από το Autologic καθώς και για να συντάσσουμε (edit) αυτά. Μπορούμε να προσθέσουμε ή να αφαιρέσουμε εξαρτήματα από την σχεδίαση. Μπορεί επίσης να ελένξει την σχεδίαση για λάθη και να παράγει αναφορές βασισμένες στην σχεδίαση.

Για να ξεκινήσει το Design Architect πληκτρολογούμε στο Unix command prompt την εντολή: pld_da.

Επιλέγουμε Design Sheet από το toolbox που βρίσκεται στα δεξιά του παραθύρου Design Architect ή κάνουμε κλικ στο Open -> Design Sheet του μενού που βρίσκεται στην κορυφή της οθόνης. Πληκτρολογούμε eddm/work/sample1 ή επιλέγουμε τον navigator όπως φαίνεται στην εικόνα 6, για να ανοίξουμε το αρχείο sheet1.

εικόνα 6

Αυτό θα ανοίξει το σχηματικό και θα το εμφανίσει στην οθόνη.

Κάνουμε κλικ στο View -> All για να ολόκληρο το σχηματικό στο παράθυρο.

Για να κάνουμε zoom σε μία συγκεκριμένη περιοχή της σχεδίασης, κρατάμε πατημένο το μεσαίο πλήκτρο του ποντικιού και μετακινούμε το ποντίκι από αριστερά προς τα κάτω δεξιά, πάνω από την περιοχή που θέλουμε να δούμε. Ελευθερώνουμε το πλήκτρο και η περιοχή που έχει επιλεγεί θα εμφανιστεί στο παράθυρο.

Τροποποίηση της σχεδίασης

Κάνουμε κλικ στο Libraries -> XACT_LIB του μενού που βρίσκεται στην κορυφή της οθόνης.

Επιλέγουμε Unified από το κουτί επιλογής βιβλιοθηκών στα δεξιά της οθόνης.

Επιλέγουμε XC4000 LIB από το κουτί επιλογής βιβλιοθηκών που βρίσκεται στα δεξιά της οθόνης.

Επιλέγουμε By Type από το κουτί επιλογής βιβλιοθηκών που βρίσκεται στα δεξιά της οθόνης.

Μπορούμε να προσθέσουμε εξαρτήματα στην σχεδίαση επιλέγοντας το εξάρτημα από την βιβλιοθήκη και τοποθετώντας το στην επιθυμητή τοποθεσία στο παράθυρο του σχηματικού. Όταν το επιθυμητό εξάρτημα έχει επιλεγεί από το κουτί επιλογής εξαρτημάτων (parts selection box), το οποίο βρίσκεται στα δεξιά της οθόνης, αυτό αυτόματα προσκολλάται στον δείκτη του ποντικιού. Για προσθέσουμε το εξάρτημα απλά μετακινούμε το ποντίκι μέχρι το highlighted εξάρτημα βρεθεί πάνω από την επιθυμητή θέση και κάνουμε κλικ το αριστερό πλήκτρο του ποντικιού. Το εξάρτημα θα προσκολληθεί μόνο του στο κύκλωμα.

Δίνοντας ονόματα στα pads

Σημείωση: Πριν τοποθετήσουμε αριθμούς στα pins, στα pads εισόδου και εξόδου, πρέπει να καθορίσουμε κατάλληλα pins που θα χρησιμοποιηθούν στο Xilinx demonstration board.

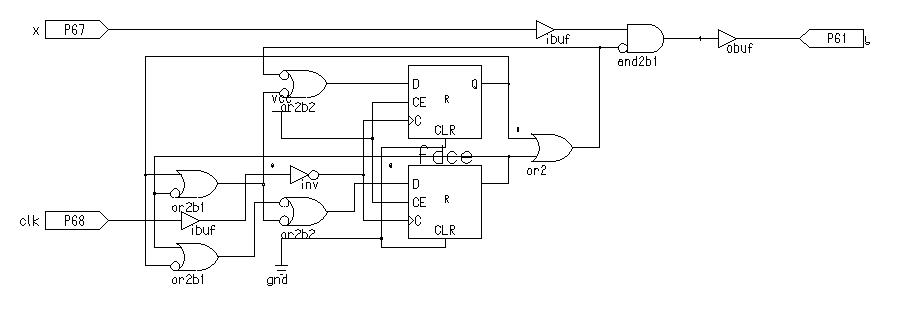

Τοποθετούμε τον δείκτη του ποντικιού πάνω στην ετικέτα (label) PXX που βρίσκεται στο pad. Πατάμε πάνω στο πληκτρολόγιο. Η ετικέτα στο pad θα υπερφωτισθεί και ένα dialοg box θα εμφανισθεί στο κάτω μέρος της οθόνης. Χρησιμοποιώντας το ποντίκι, κάνουμε κλικ στο text box και πληκτρολογούμε τον επιθυμητό αριθμό (πχ P61), και τότε πατάμε το πλήκτρο. Η εικόνα 7 δείχνει ένα σχηματικό που έχει παραχθεί από το Autologic II για το μοντέλο sample1, με εισόδους και εξόδους ορισμένες στα pins 67,68 και 61 αντίστοιχα.

εικόνα 7

Managing the project

Το Design Manager είναι ένα σύστημα διαχείρισης των αρχείων των μοντέλων που δημιουργούμε. Μπορούμε να δούμε, σβήσουμε, συντάξουμε και να διαχειριστούμε τα μοντέλα μας από αυτό το εργαλείο. Επίσης μπορούμε να ξεκινήσουμε και κάποια από τα άλλα εργαλεία της Mentor Graphics από εδώ. Για να ξεκινήσει το Design Manager πληκτρολογούμε στο Unix command prompt : pld_dmgr.

εικόνα 8

Create a Viewpoint with PLD DVE

Το πρόγραμμα PLD DVE είναι ένα εργαλείο το οποίο δημιουργεί ένα viewpoint για την σχεδίαση. Αυτά τα viewpoints χρησιμοποιούνται από το QuickSim όταν εξομοιώνουμε την σχεδίαση.

Επιλέγουμε το εικονίδιο pld_dve από το παράθυρο tools, που βρίσκεται στην αριστερή πλευρά της οθόνης και κάνουμε διπλό κλικ σε αυτό για να ξεκινήσει το πρόγραμμα PLD DVE. Ένα dialog box όπως αυτό της εικόνας 9, θα εμφανιστεί.

Πληκτρολογούμε eddm/work/sample1 στο ‘Design Object’ text box.

Επιλέγουμε “XC4000” από τις επιλογές PLD Technology.

Κάνουμε κλικ στο ΟΚ ή πατάμε το <Enter> για να αρχίσει η διαδικασία δημιουργίας των viewpoint.

εικόνα 9

Εξομοίωση της σχεδίασης με το QuickSim II

Το QuickSim II είναι ένα εργαλείο το οποίο θα διαβάσει το δικτύωμα (netlist) του σχηματικού της σχεδίασης και θα εξομοιώσει την λειτουργία του όπως αυτή θα γινόταν στο τσιπ. Είναι πολύ χρήσιμο για τον έλεγχο της λειτουργίας της σχεδίασης για να σιγουρευτούμε ότι θα μας δώσει τα επιθυμητά αποτελέσματα.

Κάλεσμα (invoke) του QuickSimII και φόρτωμα του δικτυώματος

Επιλέγουμε το εικονίδιο QuickSim II από το παράθυρο tools, στο αριστερό μέρος της οθόνης και κάνουμε διπλό κλικ σε αυτό για να ξεκινήσει το πρόγραμμα. Ένα dialog box όπως αυτό της εικόνας 10, θα εμφανισθεί.

Στο “Design Pathname” text box πληκτρολογούμε : eddm/work/sample1.

Κάνουμε κλικ στο ΟΚ ή πατάμε το <Enter> για αρχίσει το QuickSim II.

εικόνα 10

Εμφάνιση σημάτων στο παράθυρο List

εικόνα 11

εικόνα 12

Δημιουργία αρχείου Force

Ο καθορισμός των ακολουθιών των διεγέρσεων των εισόδων γίνεται εύκολα με ένα αρχείο “force file”, στο οποίο όλες οι διεγέρσεις των εσόδων είναι σε μία λίστα με ζευγάρια χρόνου-τιμής (time-value pairs). Με την χρήση ενός κειμενογράφου δημιουργούμε ένα ASCII force file παρόμοιο με το παρακάτω.

--- initialize values

force // globalsetreset 1 0

force x 0 0

force y 0 0

force clk 0 0

force state 0 0

force // globalsetreset 0 60

-- start simulation

force clk 0 60

force clk 1 80

force clk 0 100

force clk 1 120

force clk 0 140

force clk 1 160

force clk 0 180

force clk 1 200

force clk 0 220

force clk 1 240

force clk 0 260

force clk 1 280

force clk 0 300

force clk 1 320

force clk 0 340

force clk 1 360

force clk 0 380

force x 1 380

force clk 1 400

force clk 0 420

force clk 1 440

force clk 0 460

force clk 1 480

force clk 0 500

force clk 1 520

force clk 0 540

run 600

Τρέχοντας την εξομοίωση και αναλύοντας τα αποτελέσματα

Από το μενού στην κορυφή της οθόνης επιλέγουμε : Setup -> Force -> From File .

Ένα dialog box όπως αυτό της εικόνας 12 θα εμφανισθεί. Πληκτρολογούμε force_control ή χρησιμοποιούμε τον navigator για να φορτώσουμε το αρχείο και πατάμε <Enter>. Αυτό θα κάνει τον εξομοιωτή να τρέξει το force file. Οι τιμές των σημάτων θα εμφανισθούν στο παράθυρο List , όπως φαίνονται στην εικόνα 13.

εικόνα 13

Η λειτουργία του “μοντέλου” sample1 είναι να κάνει κύκλο από κατάσταση σε κατάσταση, δίνοντας μία τιμή στην έξοδο y η οποία βασίζεται στο σήμα εισόδου x. Αν η τιμή του x είναι 1 την στιγμή της μετάβασης μεταξύ των state3 και state0, η τιμή του y θα γίνει 1, αλλιώς η τιμή του y είναι 0.

Για να ελένξουμε αν η έξοδος του μοντέλου είναι σωστή, κοιτάμε τις τιμές των x και y κατά την διάρκεια της μετάβασης από κατάσταση σε κατάσταση. Το σήμα y είναι 1 μόνο όταν το x είναι 1 και state είναι 0.

Build the XC4003 Chip Design Using the Xilinx Tools

Τα εργαλεία Xilinx χρησιμοποιούνται για να προετοιμάσουν την σχεδίαση για να τρέξει στο XC4000 demonstration board.

Μετατροπή του σχηματικού στο Xilinx Netlist Format:

Στο Unix command prompt πληκτρολογούμε :

Men2xnf8 sample1 –p xc4003apc84-5 –verbose .

Αυτή η εντολή μετατρέπει το σχηματικό σε ένα EDIF netlist και κατόπιν σε Xilinx netlist XNF file.

Δημιουργία της σχεδίασης και παραγωγή ενός bitstream αρχείου:

Στο Unix command prompt πληκτρολογούμε : xmake –x sample1 .

Αυτή η εντολή τρέχει μερικά εργαλεία τα οποία χωρίζουν σε τμήματα (partition) την σχεδίαση, τοποθετούν και δρομολογούν (route) την σχεδίαση για το XC4003 PLD. Αυτή η εντολή παράγει επίσης και ένα bitstream αρχείο, το οποίο καλείται sample1.bit , το οποίο μπορεί γίνει downloaded στο XC4000 demonstration board, ώστε η σχεδίαση να μπορεί να τρέξει στο τσιπ.

Ελέγχοντας το κύκλωμα στο XC4003 Demonstration Board

Για να ελένξουμε ένα κύκλωμα στο XC4003 Demonstration Board, τα pins εισόδου και εξόδου πρέπει να συνδεθούν σε διακόπτες και LED αντίστοιχα, η σχεδίαση να φορτωθεί (download) στο board μέσω του Xchecker cable, και τότε οι διακόπτες να δώσουν διάφορα σήματα έτσι να παραχθούν επιθυμητές αποκρίσεις από το κύκλωμα.

Σύνδεση των Ι/Ο pins σε διακόπτες και LED

Download της σχεδίασης μέσω του Xchecker cable